N

naalald

Guest

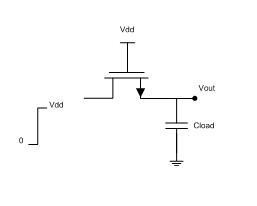

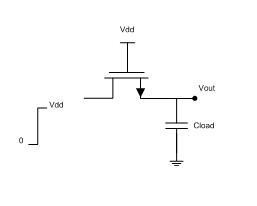

Hva foreslår du for å anslå på motstand av en bryter? Jeg tenker på å gi en Vdd til gate sin (for en enkel NMOS eller en overføring gate) og bruke en puls til inngangen. Jeg satte en kondensator Cload i produksjonen, slik

Utgangen vil følge innspill eksponentielt med en tidskonstant RC, C er kondensatoren Cload og R vil være på motstand av bryteren. Ved å beregne tiden konstant, kan vi anslå på motstand av bryteren. Hvordan er denne testen? Eventuelle andre forslag? Takk.

Utgangen vil følge innspill eksponentielt med en tidskonstant RC, C er kondensatoren Cload og R vil være på motstand av bryteren. Ved å beregne tiden konstant, kan vi anslå på motstand av bryteren. Hvordan er denne testen? Eventuelle andre forslag? Takk.